by yosikawa » 2011年2月12日(土) 19:24

ISim は起動が遅いし、それにISimが動いている間は、ISEの環境全体が重くなる。

ちょっと耐えがたいので、Veritakを試してみた。結果は良好だ。

Veritakのページ

Vectorにて4,830円。もう少し試してから買うことになりそうだ。

ロータリスイッチを使う

で作成したコードをveritakでシミュレーションしてみる。

veritakを起動する。

メニュー->Verilogプロジェクト->新しいプロジェクトを作成

ファイル名を適当に入力。

すると、対象ファイルを選択する画面になる。

t_top.v, top.v, S3E_Rotary.v を選択し、Addボタンをクリックする。

Save Projectボタンをクリックする。

Exitボタンをクリックする。

メニュー->Verilogプロジェクト->Load verilog プロジェクトを選択。

先ほどのプロジェクトファイルを再度選択する。

すると、自動的にコンパイルされる。

エラーがなければ、メッセージが緑色で表示される。

エラーがあると、白色で以下のように表示される。

この行をダブルクリックするとエディタが起動するので、修正して保存する。

再度実行するには「コンパイルします。。。。」というツールチップのアイコンをクリックする。

エラーがなければ、Goボタンをクリックする。

最初、何も起こらないと思ってしまったが、一番下のステータスバーをみるとシミュレーションがガンガン進んでいる。

Goボタンがpauseのボタンに変わるので、もう一度クリックしてシミュレーションを止める。

「Scope Tree Viewerを前面にします」という、これまた分かりにくいアイコンをクリックすると、シミュレーションの画面が表示される。

でもまだ真っ白の状態。

Scope Tree Viewの左に、テストベンチであるt_topが表示されている。

これを右クリック->「信号をWaveform Viewに追加する」->「この階層以下の信号をWaveform Viewに追加する」を選択する。

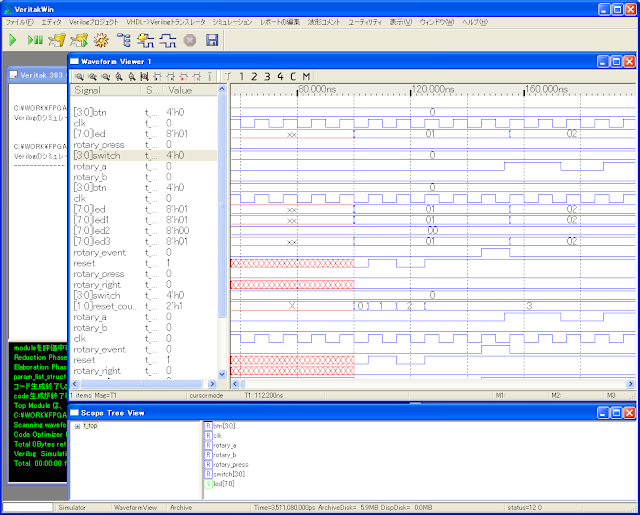

しばらくして、結果が表示される。

スケールがps単位で、ところが先ほど作ったテストベンチでは最初に100ns時間待ちをするようになっているから、

見たい部分ははるかずっと右の方だ。

画面操作方法(詳しくはveritakのホームページに詳しいチュートリアルがある)

まとめると、veritakは使える。

ちょっとへんなインタフェースだが、慣れの問題だろう。

きめ細かい設定などができて、便利そうだ。

なにより速いのは重要で、十分に実用的だと思う。

ちょっと耐えがたいので、Veritakを試してみた。結果は良好だ。

Veritakのページ

Vectorにて4,830円。もう少し試してから買うことになりそうだ。

ロータリスイッチを使う

で作成したコードをveritakでシミュレーションしてみる。

veritakを起動する。

メニュー->Verilogプロジェクト->新しいプロジェクトを作成

ファイル名を適当に入力。

すると、対象ファイルを選択する画面になる。

t_top.v, top.v, S3E_Rotary.v を選択し、Addボタンをクリックする。

Save Projectボタンをクリックする。

Exitボタンをクリックする。

メニュー->Verilogプロジェクト->Load verilog プロジェクトを選択。

先ほどのプロジェクトファイルを再度選択する。

すると、自動的にコンパイルされる。

エラーがなければ、メッセージが緑色で表示される。

エラーがあると、白色で以下のように表示される。

- コード:

C:\WORK\FPGA\Spartan-3E\T2-LED2\t-top.v(118):: Parse Error.yy=syntax error

この行をダブルクリックするとエディタが起動するので、修正して保存する。

再度実行するには「コンパイルします。。。。」というツールチップのアイコンをクリックする。

エラーがなければ、Goボタンをクリックする。

最初、何も起こらないと思ってしまったが、一番下のステータスバーをみるとシミュレーションがガンガン進んでいる。

Goボタンがpauseのボタンに変わるので、もう一度クリックしてシミュレーションを止める。

「Scope Tree Viewerを前面にします」という、これまた分かりにくいアイコンをクリックすると、シミュレーションの画面が表示される。

でもまだ真っ白の状態。

Scope Tree Viewの左に、テストベンチであるt_topが表示されている。

これを右クリック->「信号をWaveform Viewに追加する」->「この階層以下の信号をWaveform Viewに追加する」を選択する。

しばらくして、結果が表示される。

スケールがps単位で、ところが先ほど作ったテストベンチでは最初に100ns時間待ちをするようになっているから、

見たい部分ははるかずっと右の方だ。

画面操作方法(詳しくはveritakのホームページに詳しいチュートリアルがある)

- ctrlキーを押しながら、マウスのホイールを回すと横方向のスケールが変わる。

- Waveform Viewのタイトルバーを右ダブルクリックすると、時間軸の単位が変わる。

- 左クリックで時刻T1を決めるバーが現れ、右クリックでT2のパーが出る。それぞれの時刻や時間差がステータスバーに表示される。

- マウス中ボタンでメニューが出る。Enable Gridlineにチェックを付けると縦の線が表示されて、時間の関係を把握するのに役立つ。

- 目盛(80.000nsなどの時刻が表示されているところ)の上でマウスの中ボタンをクリックすると、グリッドの幅が変わる。表示->グリッドで数値で設定することもできる。

ここで分かりにくいことに、この設定画面のEnableというチェックをONにすると数値で指定した方が有効、チェックをOFFにすると、先ほどの中ボタンを使った設定が有効、という意味になる。先ほどのEnable Gridlineとは意味が違う。

まとめると、veritakは使える。

ちょっとへんなインタフェースだが、慣れの問題だろう。

きめ細かい設定などができて、便利そうだ。

なにより速いのは重要で、十分に実用的だと思う。

yosikawa » 2011年11月21日(月) 16:16

返信削除Veritak で Xilinx 用プロジェクトをシミュレーションするときに必要な、Xilinx固有の定義を読み込む設定

よく忘れるのでメモ。

1. glbl.v を追加

メニュー、Verilogプロジェクト、プロジェクトの編集 で、

ISEインストールディレクトリ/(バージョン)/ISE_DS/ISE/verilog/src/glbl.v

を選択してAddする。

2. ライブラリディレクトリを追加

同様にして、

ISEインストールディレクトリ/(バージョン)/ISE_DS/ISE/verilog/src/unisims

を選択して (フォルダアイコンの選択ではなく、フォルダの内容が表示されている状態)

Add Lib Dirボタンをクリック。

3. セーブ

Save Projectボタンを忘れずに。